集成电路中的PVD技术路线——从long...

- 深圳涛哥V

- 2025-01-18 04:02:41

集成电路中的PVD技术路线——从long throw到IMP

早期PVD工艺,由于粒子(原子或离子)到wafer表面没有较好的方向性。contact顶部接触角比底部大,而且由于侧壁对底部的遮挡效应(shadow effect),顶部沉积的原子会比底部多,会在顶部形成严重的悬凸(over hang)。

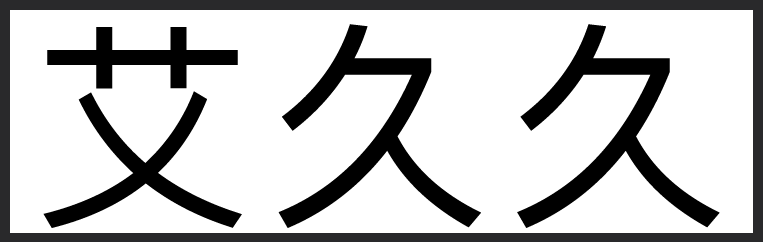

随着制程的逐渐减小,overhang的问题变得日益严重。为了解决这个问题,业界实行了两种路线(图1),一种是通过增加准直器(collimator)的方式来过滤入射角度较大的粒子,来提高底部的覆盖率,二是通过增加腔体高度的方式,增加垂直入射到wafer表面的粒子量。

2000年的时候,Applied materials推出了新一代的PVD技术,它将其命名为SIP(TM) (self-ionized plasma) PVD (physical vapor deposition) technology,其新闻稿中这样写道:”SIP腔室的新磁控溅射系统增加了腔室中金属原子的电离,这为微小的几何结构形成比较好的台阶覆盖率提供了基础。新一代的腔体还配备了具有偏置电压和更优控温性能的静电吸盘,确保了出色的热控制和最小的薄膜 overhang。“

SIP腔体(图2)在long throw的基础上使用了非平衡式磁铁(unbalanced magnetic),进一步提高了腔体等离子体的密度,并且使用了ESC(静电吸盘),Pedestal上接了RF电源以产生自偏压(bias)吸引离子。

不同于SIP,另外一种改进方式称为IMP(ionized metal plasma,图3),除了在晶圆表面增加bias牵引离子,腔体还内置了RF线圈来提高金属的离化率。对于Ti而言,IMP的离化率可以提高至40%~60%,其入射角分布最为集中(图4)。

以上是对集成电路中PVD腔体发展的简要概述,如今的PVD技术发展也已远超三言两语可以讨论清楚的范围。对于Ti来说,IMP可以将其离化率提高至40%,而对于Cu的离化率则要少的多,同时随着制程难度的不断提高以及先进封装中TSV技术的需求,PVD技术仍然在持续发展中。涨知识

早期PVD工艺,由于粒子(原子或离子)到wafer表面没有较好的方向性。contact顶部接触角比底部大,而且由于侧壁对底部的遮挡效应(shadow effect),顶部沉积的原子会比底部多,会在顶部形成严重的悬凸(over hang)。

随着制程的逐渐减小,overhang的问题变得日益严重。为了解决这个问题,业界实行了两种路线(图1),一种是通过增加准直器(collimator)的方式来过滤入射角度较大的粒子,来提高底部的覆盖率,二是通过增加腔体高度的方式,增加垂直入射到wafer表面的粒子量。

2000年的时候,Applied materials推出了新一代的PVD技术,它将其命名为SIP(TM) (self-ionized plasma) PVD (physical vapor deposition) technology,其新闻稿中这样写道:”SIP腔室的新磁控溅射系统增加了腔室中金属原子的电离,这为微小的几何结构形成比较好的台阶覆盖率提供了基础。新一代的腔体还配备了具有偏置电压和更优控温性能的静电吸盘,确保了出色的热控制和最小的薄膜 overhang。“

SIP腔体(图2)在long throw的基础上使用了非平衡式磁铁(unbalanced magnetic),进一步提高了腔体等离子体的密度,并且使用了ESC(静电吸盘),Pedestal上接了RF电源以产生自偏压(bias)吸引离子。

不同于SIP,另外一种改进方式称为IMP(ionized metal plasma,图3),除了在晶圆表面增加bias牵引离子,腔体还内置了RF线圈来提高金属的离化率。对于Ti而言,IMP的离化率可以提高至40%~60%,其入射角分布最为集中(图4)。

以上是对集成电路中PVD腔体发展的简要概述,如今的PVD技术发展也已远超三言两语可以讨论清楚的范围。对于Ti来说,IMP可以将其离化率提高至40%,而对于Cu的离化率则要少的多,同时随着制程难度的不断提高以及先进封装中TSV技术的需求,PVD技术仍然在持续发展中。涨知识